در این آموزش از سری آموزشهای گام به گام نرم افزار Hspice در مورد افزایش سرعت جمع کننده ها با استفاده از جمع کننده پیش بینی سربار (Carry look a head Adder) خواهیم پرداخت.

در ابتدا در مورد نحوه کار جمع کننده پیش بینی سربار توضیحاتی را خواهیم داد و در ادامه به شبیه سازی یک جمع کننده ۱۶ بیتی با روش مذکور پرداخته و نتایج را با جمع کننده معمولی (رقم نقلی موجی) مقایسه می کنیم و خواهیم دید که این روش در جمع کننده های طولانی (جمع کننده با تعداد بیت زیاد) چقدر می تواند در کاهش تاخیر جمع کننده که به معنی افزایش سرعت آن می باشد تاثیر گذار باشد.

جمع کننده پیش بینی رقم نقلی

افزایش سرعت عملکرد مدارات دیجیتال همواره مورد بحث بوده و یکی از حوزه های فعال پژوهشی چه در گذشته و چه در حال حاضر می باشد. جمع کننده یکی از بلوک های اصلی مدارات دیجیتال بوده و در پردازنده های دیجیتال مانند cpu ها نقش اساسی دارد. و به نحوی می توان گفت سرعت عملکرد جمع کننده بر روی عملکرد کلی سیستم تاثیری انکار ناپذیر خواهد داشت.

یکی از روش های مرسوم برای افزایش سرعت جمع کننده ها پیش بینی کردن carry با استفاده از جمع کننده پیش بینی رقم نقلی می باشد.

در این روش بر خلاف جمع کننده رقم نقلی موجی (RCA) که هر تمام جمع کننده منتظر آمدن رقم نقلی طبقه قبلی می ماند ، ما یک مدار مستقل برای پیش بینی رقم نقلی بر اساس ورودی ها خواهیم داشت و چون رقم نقلی به طور مستقل تولید می شود نیازی به تمام جمع کننده که سه ورودی دارد (ورودی های a,b مربوط به بیت های ورودی جمع کننده و ورودی c مربوط به رقم نقلی طبقه قبلی است) نخواهیم داشت.

و عمل جمع توسط مدار پیش بینی رقم نقلی به علاوه نیم جمع کننده و گیت XOR (که حاصلجمع خروجی نیم جمع کننده و رقم نقلی تولید شده توسط مدار پیش بینی رقم نقلی را عهده دار است) انجام خواهد شد.

با این روش تاخیر مدار به طور چشم گیری کاهش پیدا خواهد کرد ، اما این روش را نمی توان برای مدار با هر تعداد بیتی انجام داد و وقتی که تعداد بیت ها زیاد می شود مداری که برای پیش بینی رقم نقلی در جمع کننده پیش بینی سربار مورد نیاز است بسیار پیچیده تر شده و تاخیر عملکرد آن به قدری افزایش می یابد که از زمان انتظار برای دریافت رقم نقلی طبقه ماقبل بیشتر می شود.

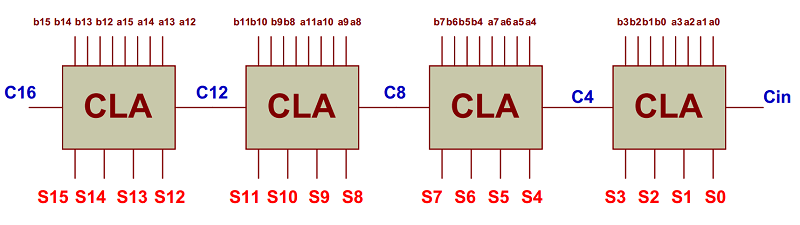

در عمل این روش را تا ۵ بیت هم به کار می برند اما برای تعداد بیت های بیشتر از پنج از سایر روش های دیگر برای افزایش سرعت استفاده می کنند. به طور تجربی بهینه ترین حالت برای جمع کننده پیش بیتی رقم نقلی ۴ بیت می باشد. و اگر بخواهیم یک جمع کننده مثلاً شانزده بیت را با این روش پیاده سازی کنیم از چهار جمع کننده پیش بینی رقم نقلی چهار بیتی پشت سر هم به شکل زیر استفاده خواهیم نمود.

البته همانطور که گفتیم این روش را می توان تا ۵ بیت هم اجرا نمود مثلا همین جمع کننده پیش بینی سربار ۱۶ بیتی را می توان با سه جمع کننده ۵ بیتی به علاوه یک جمع کننده تک بیتی اجرا کرد ولی تجربه نشان می دهد که حالت اول نتیجه بهتری می دهد و تاخیر کمتری را خواهیم داشت. به علاوه در همه طراحی ها باید به چینش (Lay out) مدار هم توجه نمود. حالت اولی چینش منظم تری نسبت به حالتی که سه جمع کننده پنج بیتی با یک جمع کننده تک بیتی پشت سر هم قرار گیرند خواهد داشت.

نکته ۱: جمع کننده هایی که در عمل ساخته می شوند به صورت توانی از ۲ هستند برای همین ما مثال ۱۶ بیت را که جنبه عملی دارد معرفی نمودیم ، ولی امکان ساخت جمع کننده با هر تعداد بیتی امکان پذیر است.

ساختار مدار پیش بینی سربار

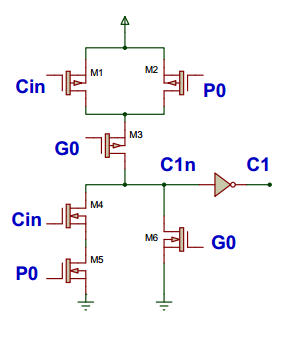

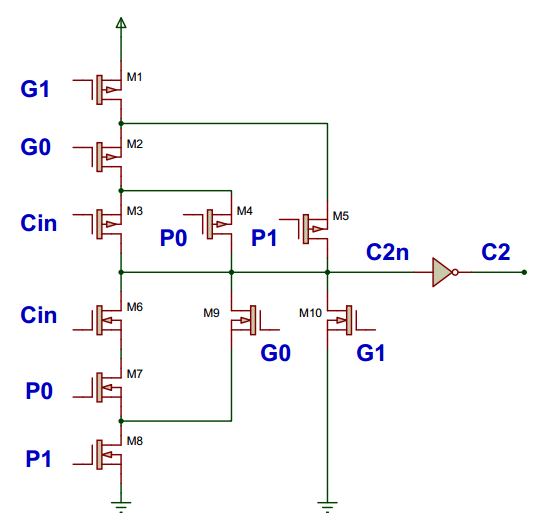

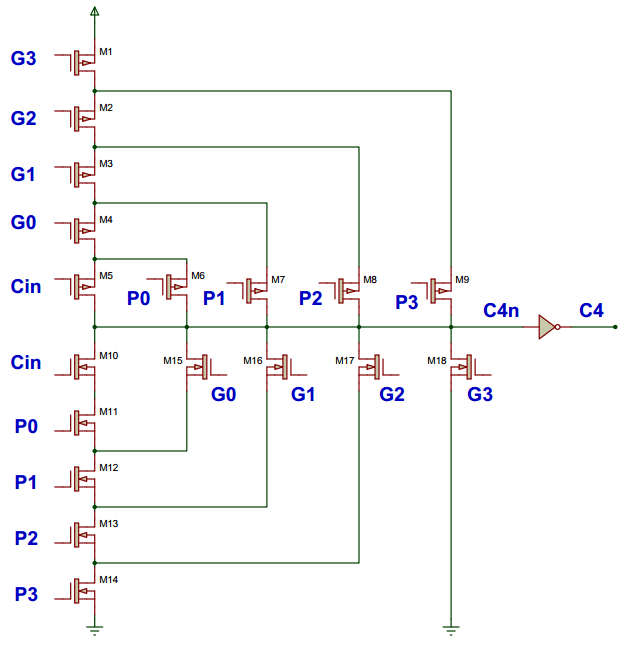

مدار پیش بینی رقم نقلی برای تولید C1,C2,C3,C4 در یک جمع کننده پیش بینی سربار به ترتیب در شکل های زیر نشان داده شده است.

اگر یکی از این مدارهای پیش بینی رقم نقلی جمع کننده پیش بینی سربار را در نظر بگیریم می بینیم که از تعدادی ترانزیستور تشکیل شده است که در ترکیب خاصی از ورودی های P , G خروجی C برابر یک خواهد.

به عنوان مثال اگر شرایطی را که تحت آن C4 برابر یک می شود در نظر بگیریم ، می بینیم در صورتی که هر کدام از حالات زیر اتفاق بیفتد C4n توسط مدار pull down network به پایین کشیده شده و متقابلاً C4 که not شده C4n است بالا خواهد رفت و خروجی گیت not به سمت ولتاژ تغذیه یعنی یک منطقی میل خواهد کرد.

G3=1

G2.P3=1

G1.P2.P3=1

G0.P1.P2.P3=1

Cin.P0.P1.P2.P3=1

نکته ۲: علامت . به معنای AND (و) منطقی است یعنی شرایطی که هر دو ، هر سه یا همه ورودیها همزمان با هم یک شوند. مثلاً G1.P2.P3=1 یعنی اگر G1 , P2 , P3 با همزمان با هم بالا (High) بودند یک مسیر جریان از طریق ترانزیستورهای مربوطه (M13,M14,M16) برقرار باشد.

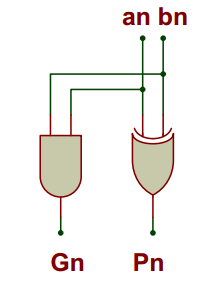

نکته ۳: بیت های P, G در اصل از خروجی نیم جمع کننده ها حاصل می شوند. اگر یک نیم جمع کننده را به شکل زیر در نظر بگیریم دو ورودی به آن اعمال خواهد شد که بالا رفتن خروجی گیت AND به معنای تولید رقم نقلی (Generate) و بالا رفتن خروجی گیت XOR به معنای انتشار (Propagate) عمل جمع دو بیت به ورودی گیت XOR نهایی که خروجی جمع کننده را تشکیل می دهد می باشد.

نکته ۴: ورودی های گیت XOR نهایی شامل خروجی انتشار نیم جمع کننده Pn و رقم نقلی خروجی طبقه قبلی Cn-1 است و همانطور که گفته شد خروجی آن حاصلجمع نهایی را مشخص می کند.

نوشتن نت لیست جمع کننده پیش بینی سربار ۱۶ بیتی

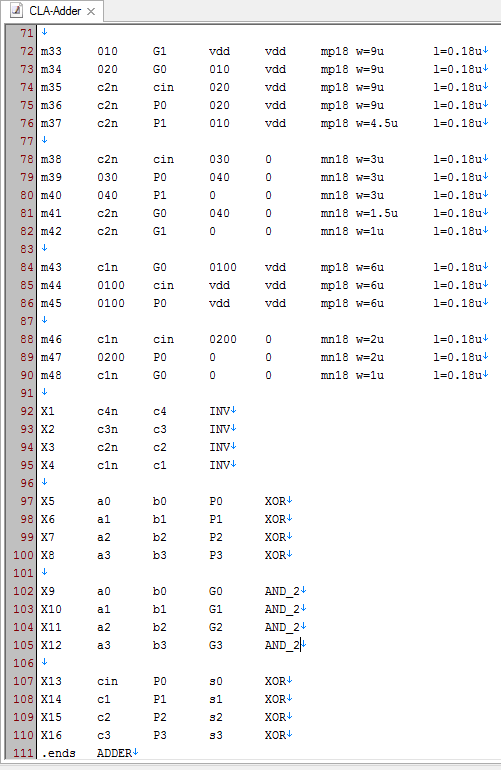

برای نوشتن نت لیست جمع کننده پیش بینی سربار ۱۶ بیتی می توانیم یک جمع کننده ۴ بیتی را به صورت زیر مدار در آورده (همانطور که قبلا گفتیم ۴ بیت بهینه ترین حالت است) و آن را چهار بار تکرار کنیم. نحوه نوشتن نت لیست در شکل های زیر به ترتیب دیده می شود.

نوشتن نت لیست مدار جمع کننده پیش بینی سربار با استفاده زیر مدارات کار سختی نبوده و در جلسات گذشته مثال های زیادی در مورد زیرمدارات گفته شده و نیازی به تکرار مکررات نیست تنها نکته مهمی که در این جلسه نیاز به توضیح و تفسیر دارد نحوه سایز بندی ترانزیستورها می باشد که مقداری متفاوت تر از آن چیزی است که قبلاً بررسی نمودیم.

باز در اینجا نحوه سایز بندی یکی از مدارات تولید رقم نقلی به عنوان نمونه C4 را مورد بررسی قرار می دهیم و آن را به بقیه مدارات دیگر تعمیم خواهیم داد. همانطور که در جلسات گذشته نیز اشاره نمودیم هنگامی که n ترانزیستور بر روی هم سوار می شوند (به صورت سری با هم قرار می گیرند) سایز آنها n برابر خواهد شد اما در حالت موازی سایز را تغییر نمی دهیم.

در این مثال (مدار تولید C4) حداکثر تعداد ترانزیستورهای سری شده با هم ۵ عدد می باشد پس سایز مبنا را که برای nmos=1u و برای pmos=3u در نظر گرفته بودیم را در ۵ ضرب می کنیم. پس با این حساب سایز ترانزیستورهای M1-M6 برابر ۱۵um و سایز ترانزیستورهای M10-M14 برابر ۵um به دست خواهد آمد. حال سوال اینجاست که تکلیف بقیه ترانزیستورها چه می شود؟

برای سایز بندی بقیه ترانزیستورهای مدار تولید Carry جمع کننده پیش بینی رقم نقلی باید کاری کنیم که trise , tfall مسیرهای موازی برابر شود یعنی مقاومتی که جریان در مسیرهای موازی می بیند یکسان باشد که این کار با تغییر سایز ترانزیستورها ممکن است ، مثلاً ترازیستور PMOS ، M7 را در نظر بگیرید که با دو ترانزیستور سری M4 , M5 به صورت موازی قرار گرفته است.

وقتی جریانی از VDD به سمت نود میانی C5n جاری می شود (خواه از مسیر مقاومت های سری M4,M5 جاری شود و خواه از مسیر M7) باید مقاومت یکسانی را در هر دو مسیر ببیند و چون M7 با دو ترانزیستور که سایز هر کدام از آنها برابر ۱۵um است به صورت موازی قرار گرفته و ما می دانیم سایز ترانزیستور با مقاومت آن در برابر جریان نسبت عکس دارد پس برای اینکه مقاومت مسیر M7 برابر مقاومت مسیر M4 , M5 شود سایز آن را نصف سایز ترانزیستورهای سری شده با هم قرار می دهیم.

یا مثلاً سایز M8 را که با سه ترانزیستور سری با هم موازی شده یک سوم ۱۵um یعنی برابر ۵um انتخاب خواهیم کرد. برای بقیه ترانزیستورهای مدار تولید Carry جمع کننده پیش بینی سربار هم به همین شکل تا آخر ادامه می دهیم.

نتایج شبیه سازی جمع کننده CLA 16 بیتی و مقایسه با RCA

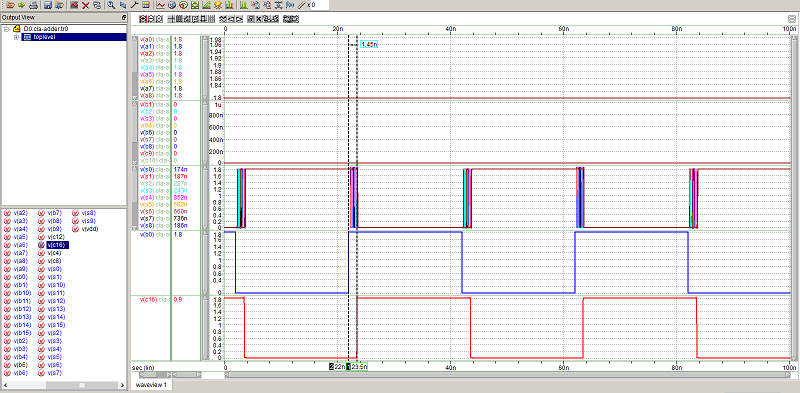

برای تست سرعت جمع کننده پیش بینی سربار باید تاخیر مسیر بحرانی مدار را اندازه گرفت که تاخیر با سرعت نسبت عکس دارد. مسیر بحرانی به ورودی گفته می شود که باعث ایجاد بیشترین تاخیر در مدار خواهد شد ، که در جمع کننده سربار نردبانی که قبلاً بررسی نمودیم و جمع کننده پیش بینی سربار مسیر بحرانی در صورتی اتفاق می افتد که رقم نقلی از کم ارزش ترین بیت به با ارزش ترین بیت (در اینجا یعنی C16 ) منتقل شود.

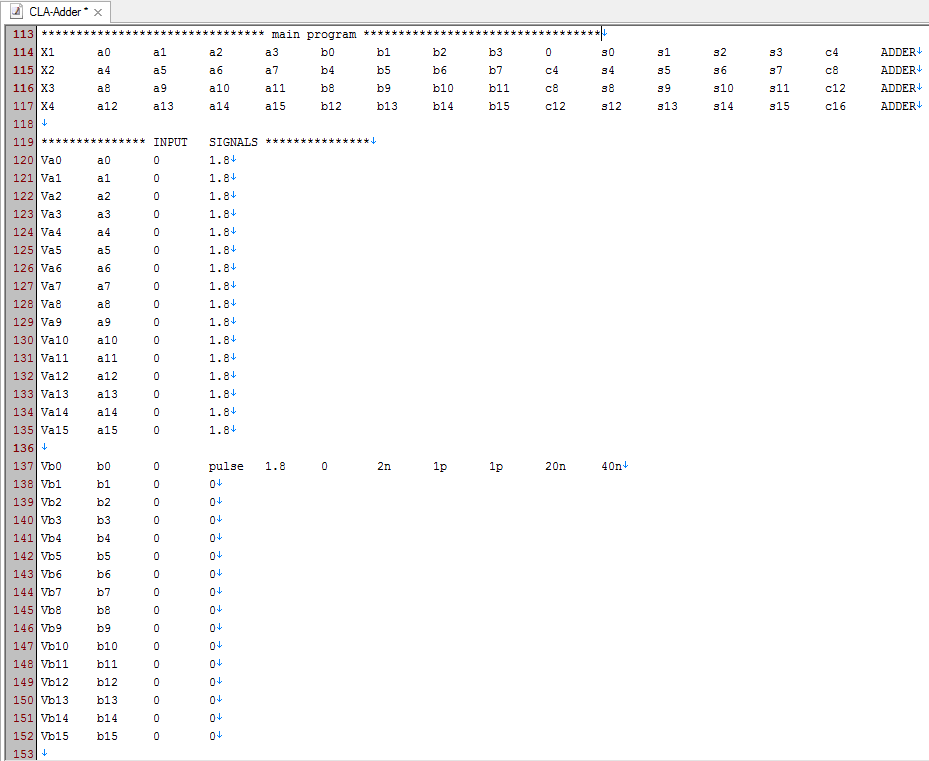

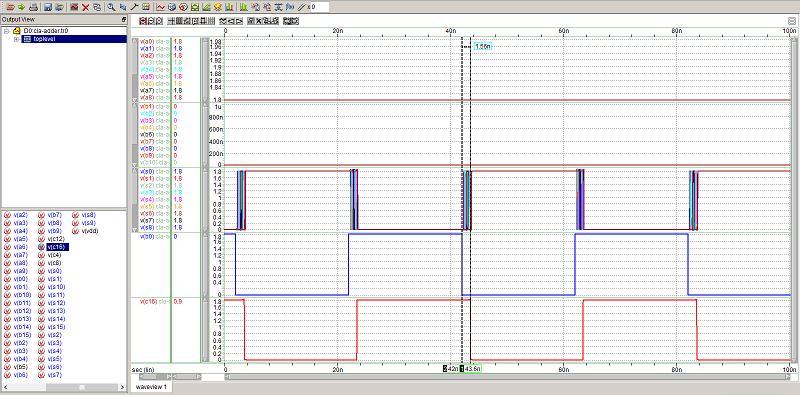

پس هنگامی که ورودی های a0-a15 را تماماً برابر یک منطقی قرار می دهیم و ورودی های b1-b15 را برابر صفر و ورودی b0 را به صورت پالسی تعریف می کنیم هنگامی که ورودی b0 از حالت Low به High و بلعکس تغییر وضعیت می دهد مسیر بحرانی اتفاق می افتد. نتیجه شبیه سازی یک جمع کننده پیش بینی سربار ۱۶ بیتی را در شکل های زیر به ازای مسیر بحرانی در هر دو وضعیت Low به High و بلعکس مشاهده می کنیم.

نتایج شبیه سازی جمع کننده پیش بینی سربار مقادیر ۱٫۴۵nsec و ۱٫۵۶nsec را برای برای هر دو وضعیت بالا و پایین بیت C16 نشان می دهد که این به ما می گوید بیشترین تاخیر این جمع کننده که از رابطه tr+tf/2 به دست می آید در حدود ۱٫۵nsec است پس سرعت جمع کننده پیش بینی سربار ۱۶ بیتی با این مشخصات و این تکنولوژی (۰٫۱۸um) و این نحوه سایز بندی در حدود ۶۶۷Mhz =1/1.5nsec به دست می آید.

همین مراحل را برای جمع کننده سربار نردبانی تکرار کردیم متوسط تاخیر مدار حدود ۳nsec به دست آمد که نوشتن نت لیست و شبیه سازی آن را به عنوان تمرین به خواننده واگذار می کنیم.

دیدیم که با استفاده از این تکنیک سرعت مدار در یک جمع کننده با تعداد بیت های مشابه حدود ۲ برابر افزایش یافت که این افزایش سرعت در ازای پیچیده تر شدن مدار و افزایش توان مصرفی بدست آمد. بنابراین برای بهبود یک پارامتر (در اینجا سرعت) باید سایر پارامترها را تا حدودی نادیده بگیریم و این مصالحه (trade off) هنر طراح مدارات مجتمع می باشد که بسته به مشخصات مدار و پارامترهای مورد نیاز باید یک یا چندین پارامتر را فدای بقیه پارامترها کرد.

برای دریافت مشاوره انجام پروژه های دانشگاهی وارد صفحه انجام پروژه hspice سایت استاد راهنما شوید.