در این آموزش از سری آموزشهای گام به گام نرم افزار Hspice در مورد افزایش سرعت جمع کننده ها با استفاده از تکنیک جمع کننده پرش سربار (Carry skip adder) خواهیم پرداخت.

در ابتدا توضیحات مختصری از جمع کننده پرش سربار و دلیل انتخاب آن در جمع کننده هایی با تعداد بیت های طولانی (Long Adders) را ارائه خواهیم نمود و در بخش های بعدی نوشتن نت لیست و شبیه سازی این جمع کننده را بررسی کرده و تاخیر آن را با جمع کننده های سربار نردبانی و پیش بینی سربار مقایسه خواهیم کرد.

جمع کننده پرش سربار

در این روش در صورتی که تاخیر جمع کننده به وضعیت کم ارزش ترین بیت مدار وابسته باشد (مسیر بحرانی) رقم نقلی از مسیری جداگانه عبور کرده و پرش خواهد کرد و دلیل نامگذاری این نوع جمع کننده هم به همین علت است. نام دیگر این جمع کننده جمع کننده کنار گذر سربار (Carry Bypass adder) می باشد چون همانطور که گفته شد سربار یا همان رقم نقلی بسته به شرایط امکان دارد از مسیر عادی خود تغییر جهت داده و مسیری جداگانه را در پیش گیرد.

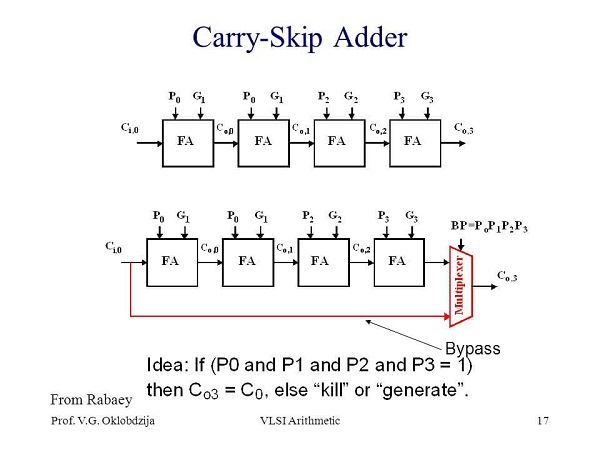

شکل زیر یک ADDER چهار بیتی را نشان می دهد که در آن از تکنیک جمع کننده کنار گذر سربار استفاده شده است.

همانطور که مشاهده می کنید در جمع کننده معمولی در صورتی که همه سیگنالهای انتشار (P0,P1,P2,P3) بالا باشند نیاز است تا رقم نقلی ورودی جمع کننده (Ci,0) از تک تک تمام جمع کننده ها (F.A) به صورت موجی عبور کند و این به معنی ایجاد مسیر بحرانی (مسیری که بیشترین تاخیر را در مدار به وجود می آورد) در این مدار است.

راه کاری که در جمع کننده پرش سربار برای حل این مشکل اندیشیده شده است این است که ما یک مدار اضافی برای تشخیص وقوع این حالت تعبیه کنیم به گونه ای که اگر حالت گفته شده اتفاق افتاد رقم نقلی به جای اینکه از تک تک جمع کننده ها عبور کند و مسیر طولانی طی شود از مسیری میان بر (خط قرمز رنگ Bypass) به طبقه بعدی انتقال یابد. این کار با اضافه کردن مالتی پلکسر و گیت AND به سادگی امکان پذیر است.

در صورتی که شرایط بحرانی در مدار ایجاد شود تمامی سیگنالهای انتشار بالا رفته که نتیجتاً بالا رفتن خروجی گیت AND را در پی خواهد داشت و خروجی گیت AND نیز که به خط کنترل مالتی پلکسر دو به یک ۲*۱ MUX متصل است باعث می شود ورودی دوم مالتی پلکسر که به رقم نقلی ورودی متصل است انتخاب شود با این روش رقم نقلی هر چه که باشد به جای عبور از تک تک تمام جمع کننده ها از طریق مسیر Bypass و مالتی پلکسر به طبقه بعدی پرش خواهد کرد.

اما اگر ورودی هر حالت دیگری داشته باشد (به غیر از حالتی که سیگنالهای انتشار همگی بالا باشند) مدار به شکل معمول خود و به صورت موجی رقم نقلی را انتقال خواهد داد و مسیر رقم نقلی از طریق تمام جمع کننده ها و مالتی پلکسر بسته خواهد شد.

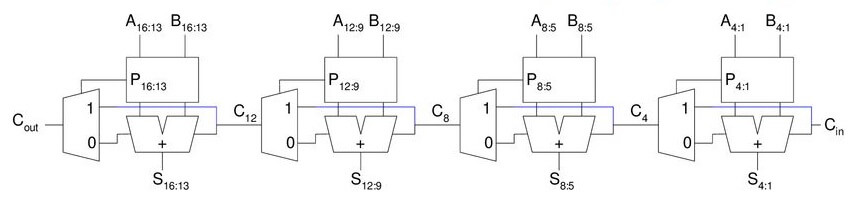

نکته مهم در اینجا این است که اگر تعداد بیت ها از چهار عدد بیشتر شود تاخیر گیت AND با بیش از چهار ورودی بسیار بالا رفته و کل محاسن جمع کننده کنار گذر سربار از بین می رود ، پس بهینه ترین حالت ممکن همان چهار بیت بوده و معمولاً تعداد بیتهای کمتر و بیشتر از ۴ به ندرت استفاده می شود ، البته این مساله قطعی نیست و امکان استفاده از تعداد بیت های دلخواه وجود دارد.

پس دیدیم که با اضافه کردن چند مدار ساده توانستیم تاخیر مدار را کاهش داده که نتیجه آن افزایش سرعت مدار جمع کننده پرش سربار در ازای مصرف توان بیشتر و پیچیده تر شدن مدار است که در جمع کننده های طولانی تر این افزایش سرعت بیشتر به چشم می آید.

نکته۱: برای تولید سیگنال انتشار (Propagate) نیازی به استفاده از مدار اضافه که همان گیت XOR است نمی باشد چون در ساختار تمام جمع کننده به طور طبیعی سیگنال انتشار تولید می شود و می توانیم از آن استفاده کنیم.

نکته۲: ساختار مالتی پلکسر با استفاده از transmission gate طراحی شده است چون این ساختار برای مالتی پلکسرهای ۲*۱ ساده ترین مدار ممکن می باشد و به دلیل سادگی مدار از توضیح دادن آن صرفه نظر می کنیم و تحلیل را به خواننده واگذار خواهیم کرد.

نوشتن نت لیست و شبیه سازی

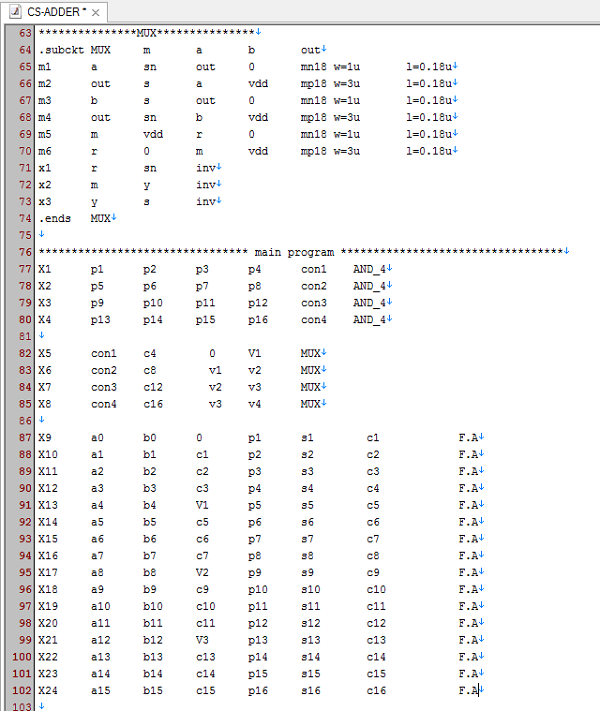

نت لیست یک جمع کننده پرش سربار ۱۶ بیتی به شکل زیر است. نکته ای که در این نت لیست حایز اهمیت می باشد این است که در تعریف تمام جمع کننده ها به صورت زیر مدار تعداد خروجی ها یکی اضافه شده است و برای تولید سیگنال انتشار که از گیت های XOR حاصل می شود از خروجی گیت های XOR داخل همان تمام جمع کننده استفاده کرده و با این کار در مصرف مدارات اضافه صرفه جویی نموده ایم.

البته با این کار تاخیر تمام جمع کننده مقدار بسیار کمی افزایش می یابد و دلیل آن ضافه شدن خازن مدار گیت AND به نودهای داخلی مدار تمام جمع کننده است که زیاد به چشم نمی آید.

نکته۳: در تعریف مالتی پلکسر به صورت زیر مدار نیز از یک مدار همسان ساز تاخیر استفاده شده به گونه ای که برای اینکه تاخیر خط کنترلی S با Sbar یکی شود از دو گیت not و یک transmission gate اضافه برای همزمان سازی اعمال سیگنال کنترلی استفاده کرده ایم.

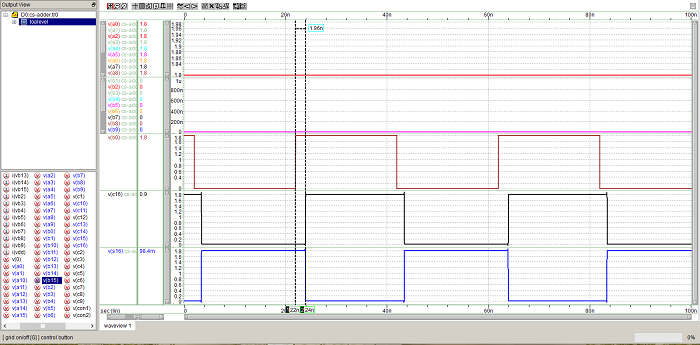

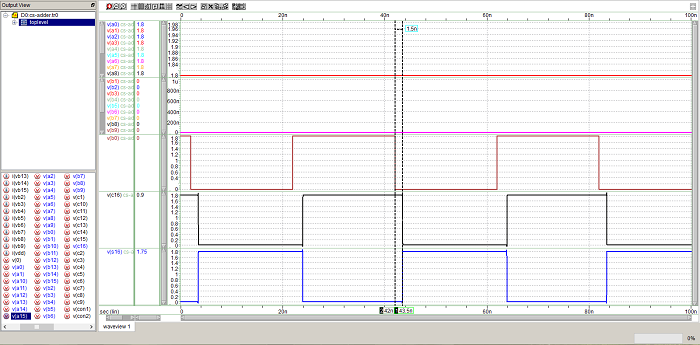

اشکال زیر نتایج شبیه سازی جمع کننده کناگذر سربار را به ازای ورودی بحرانی نشان می دهد همان کاری که برای محاسبه تاخیر در مدارات قبلی (جمع کننده پیش بینی سربار و جمع کننده سربار نردبانی) انجام دادیم را اینجا نیز تکرار خواهیم کرد.

نتایج شبیه سازی تاخیری حدود ۱٫۷۳nsec را برای یک جمع کننده ۱۶ بیتی پرش سربار نشان می دهد که در مقایسه با جمع کننده سربار نردبانی (۳nsec) اوضاع به مراتب بهتر بوده و اگر با جمع کننده پیش بینی سربار (۱٫۵nsec) بخواهیم مقایسه کنیم کمی تاخیر افزایش داشته است ولی در عوض مدار ساده تر بوده و مصرف توان نیز مقداری کاهش یافته است.

اما نکته مهمی که باید به آن توجه داشته باشیم این است که این مقایسه برای حالت ۱۶ بیتی بوده و ممکن است برای تعداد بیت های بیشتر مثلاً ۳۲ یا ۶۴ بیت نتایج شبیه سازی دو جمع کننده کنار گذر سربار و پیش بینی سربار متفاوت از نتیجه باشد که اکنون به دست آوردیم. به هر حال در طراحی مدارات هیچ قطعیتی وجود ندارد و همه چیز به شرایط و مشخصات مدار بستگی دارد.

به عنوان نتیجه گیری کلی از مسایل مربوط به جمع کننده ها می خواهیم بگوییم که می توان جمع کننده های مختلف را با هم ادغام نموده و به سرعت و توان های معقولی رسید ، کاری که در مقالات مربوط به این حوزه انجام می شود.

برای دریافت مشاوره انجام پروژه های دانشگاهی وارد صفحه انجام پروژه hspice سایت استاد راهنما شوید.